In Proceedings of the 1990 International Conference on Parallel Processing, 1990.ĭavid V. Reducing memory and traffic requirements for scalable directory-based cache coherence schemes. IEEE Transactions on Software Engineering, 16(6):660–673, June 1990.Īnoop Gupta, Wolf-Dietrich Weber, and Todd Mowry. Memory access dependencies in sharedmemory multiprocessors. In Proceedings of the 17th International Symposium on Computer Architecture, pages 60–68, 1990. A new solution to coherence problems in multicache systems. In Proceedings of the 1985 International Conference on Parallel Processing, pages 782–789, 1985. ACM Transactions on Computer Systems, 4(4):274–298, November 1986. Cache coherence protocols: Evaluation using a multiprocessor simulation model. In Proceedings of the 15th International Symposium on Computer Architecture, pages 281–289, 1988. An evaluation of directory schemes for cache coherence. The consistency of shared-bus protocols is shown to be naturally stronger than that of non-bus protocols.The first protocol of its kind is presented for a large hierarchical multiprocessor, using a bus-based protocol within each cluster and a general protocol in the network connecting the clusters to the shared main memory.Anant Agarwal, Richard Simoni, John Hennessy, and Mark Horowitz. Coherence is compared and contrasted with other levels of consistency, which are also identified. All new protocols have been proven correct one of the proofs is included.Previous definitions of cache coherence are shown to be inadequate and a new definition is presented.

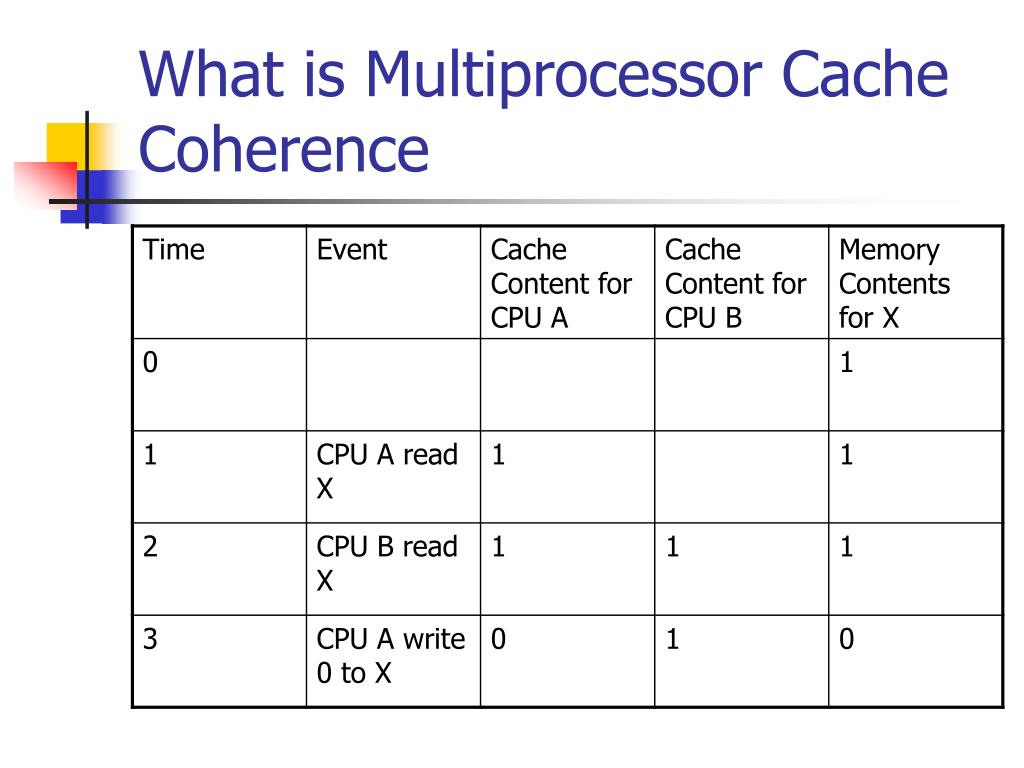

A new class of protocols is presented that offers reduced implementation cost and expandability, while retaining a high level of performance, as illustrated by simulation results using a crossbar switch. The simulation model and parameters are described in detail.Previous protocols for general interconnection networks are shown to contain flaws and to be costly to implement. In each category, a new protocol is presented with better performance than previous schemes, based on simulation results. In invalidation protocols all other cached copies must be invalidated before any copy can be changed in distributed write protocols all copies must be updated each time a shared block is modified. Previously proposed shared-bus protocols are described using uniform terminology, and they are shown to divide into two categories: invalidation and distributed write. This dissertation explores possible solutions to the cache coherence problem and identifies cache coherence protocols-solutions implemented entirely in hardware-as an attractive alternative.Protocols for shared-bus systems are shown to be an interesting special case. The cache coherence problem is keeping all cached copies of the same memory location identical. Adding a cache memory for each processor reduces the average access time, but it creates the possibility of inconsistency among cached copies. However, sharing memory between processors leads to contention which delays memory accesses. Shared-memory multiprocessors offer increased computational power and the programmability of the shared-memory model.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed